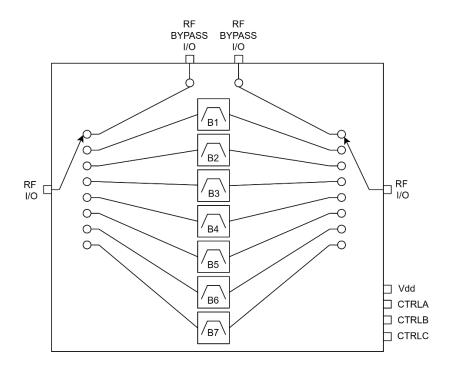

### **Product Description**

ATEK950P6 is a sub-octave switchable filter bank covering 485 - 8000 MHz frequency band. Filterbank consists of an SP8T switch followed by 7 fixed frequency band pass filters which are followed by another SP8T switch. 8<sup>th</sup> arms of each SP8T switch are used to send the input/output signals to 2 pins. This allows users to bypass the filterbank off-chip. Alternatively, additional off-chip filter or filterbanks can be implemented by using the bypass feature.

RF Input and Outputs are internally matched to 50 ohms for ease of use.

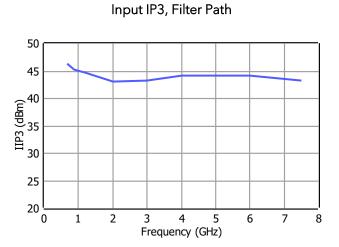

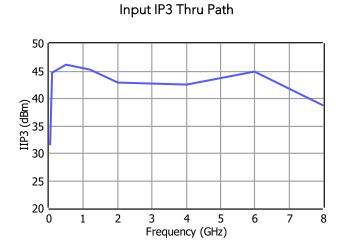

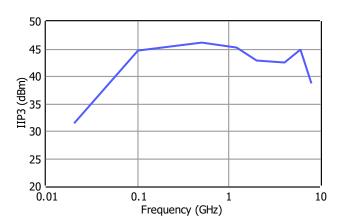

Filterbank provides 43 dBm IIP3 which allows users to realize high dynamic range wideband receiver frontends. Sub-octave filterbank architecture improves overall system IIP2.

Filterbank is housed in 6x6 mm low-cost surface mount package.

Evaluation Board, custom package and module options are available upon request.

#### **Product Features**

- Frequency Range: 485 8000 MHz

- 7 Switchable Band Pass Filters

- IIP3: 43 dBm

- Single Supply: 3.3 V to 5 V

### **Applications**

- Test Equipment

- Electronic Warfare

- Wideband Receivers

- Spectrum Analysis

- SDR

### **Functional Block Diagram**

1 of 12

# **Electrical Specifications**

Test conditions unless otherwise noted:  $V_{dd} = +5 V$ , T = 25 C.

| Parameter                        | Min                  | Тур  | Max         | Units |     |

|----------------------------------|----------------------|------|-------------|-------|-----|

| Frequency Range                  | 2                    |      | 8000        | MHz   |     |

| 3dB Bandwidth                    | Band 1               |      | 485 - 810   |       | MHz |

| (High Pass 3dB cutoff - Low Pass | Band 2               |      | 670 - 1125  |       |     |

| 3dB cutoff)                      | Band 3               |      | 960 - 1670  |       |     |

|                                  | Band 4               |      | 1440 - 2560 |       |     |

|                                  | Band 5               |      | 2140 - 3850 |       |     |

|                                  | Band 6               |      | 3300 - 5880 |       |     |

|                                  | Band 7               |      | 4820 - 8500 |       |     |

|                                  | External Bypass      |      | 2-9000      |       |     |

| Insertion Loss                   | Filter Paths         |      | 6           |       | dB  |

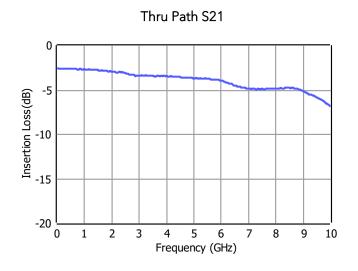

|                                  | External Bypass Path |      | 3           |       |     |

| Input IP3                        |                      | 43   |             | dBm   |     |

| Switching Speed                  |                      | 150  |             | nS    |     |

| Logic Level                      | Low                  | -0.1 |             | 0.5   | V   |

|                                  | High                 | 2    |             | 5     |     |

| DC Supply Voltage                |                      | 3.2  | 5           | 5.5   | V   |

| DC Supply Current                |                      | 15   |             | mA    |     |

| Operating Temperature            | -40                  |      | 85          | °C    |     |

2 of 12

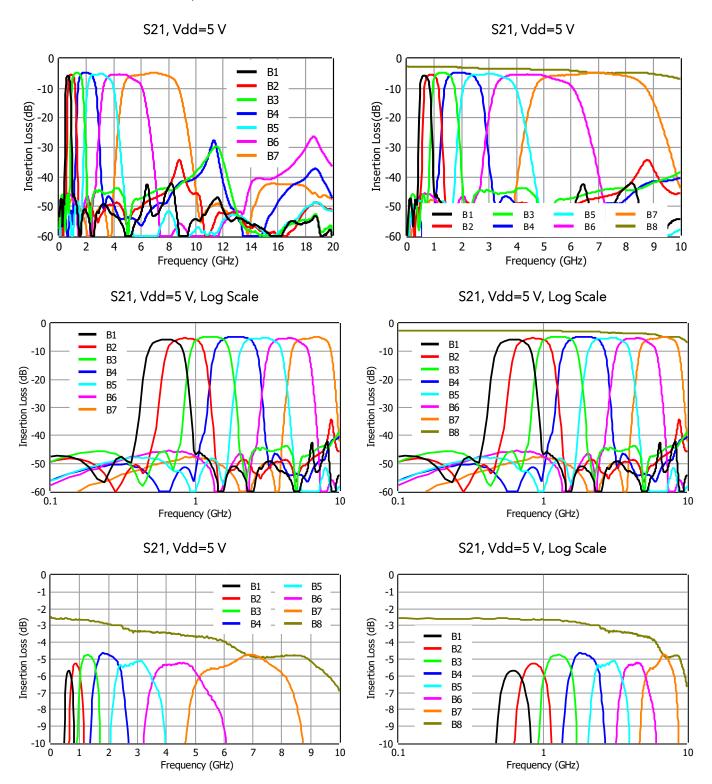

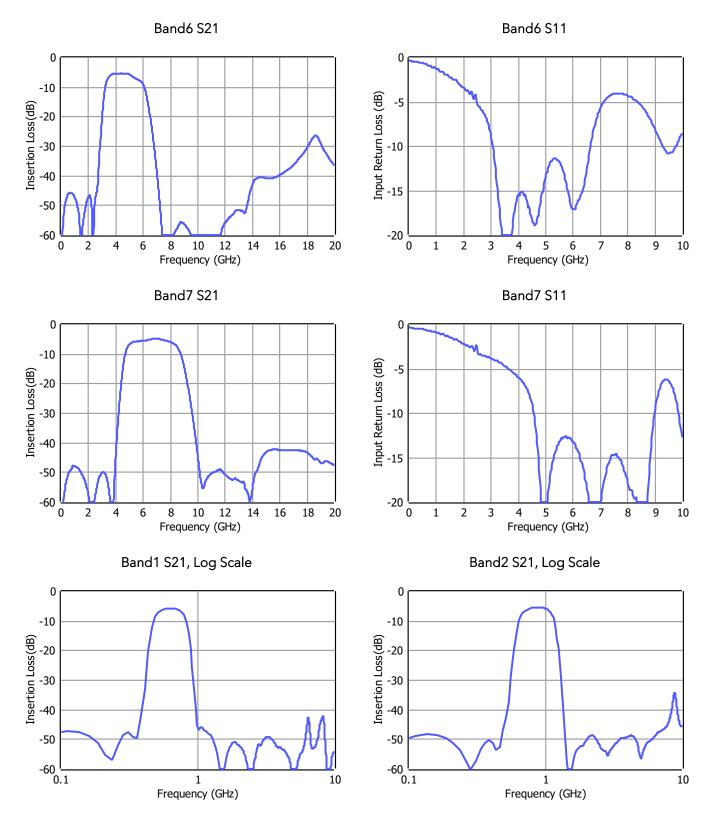

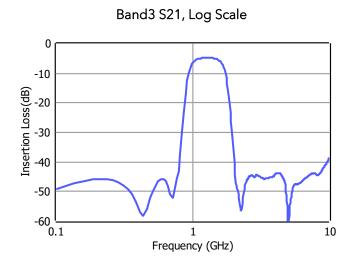

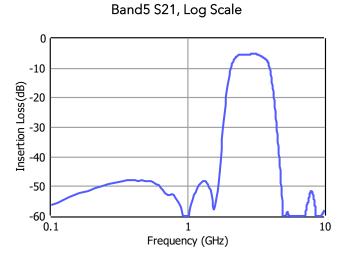

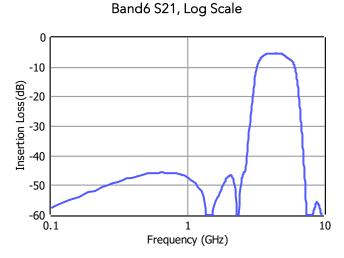

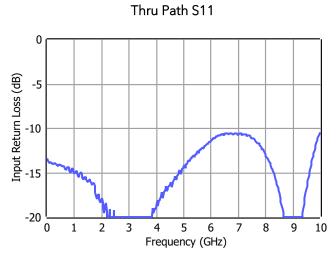

Conditions unless otherwise specified:  $V_{dd} = +5 V$ , T = 25 C.

Conditions unless otherwise specified:  $V_{dd} = +5 V$ , T = 25 C.

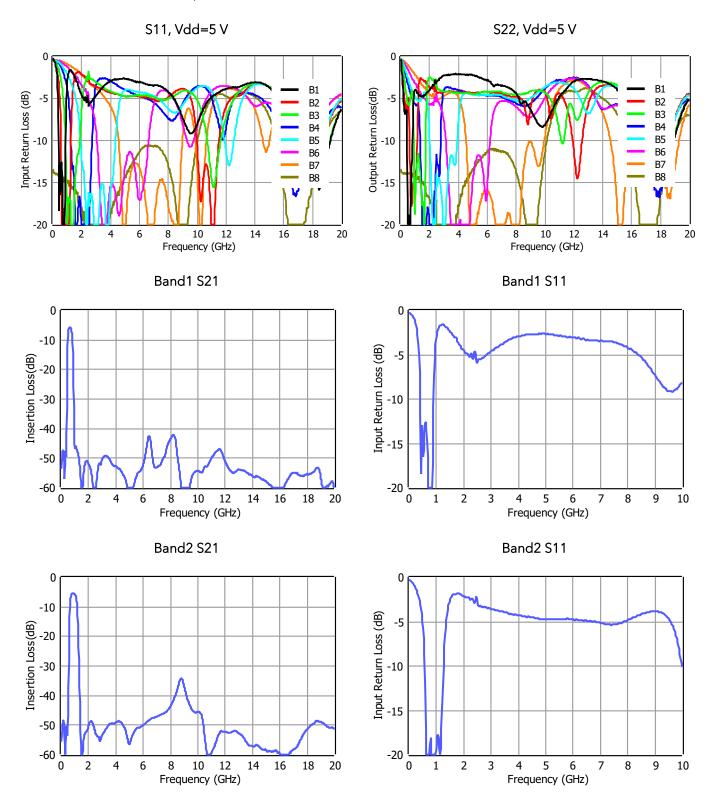

Conditions unless otherwise specified:  $V_{dd} = +5 \text{ V}$ , T = 25 C.

Conditions unless otherwise specified:  $V_{dd} = +5 \text{ V}$ , T = 25 C.

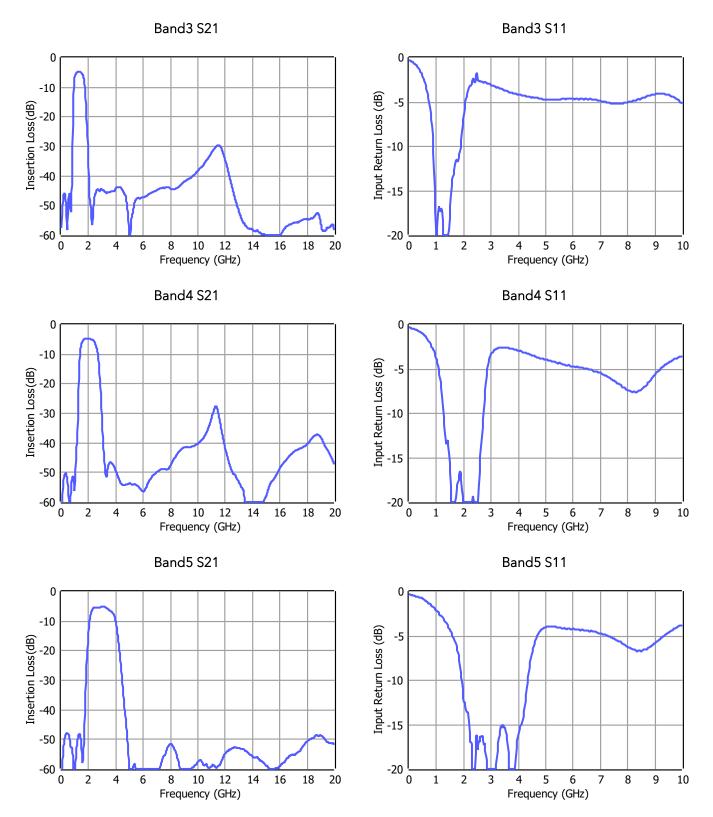

Conditions unless otherwise specified:  $V_{dd} = +5 V$ , T = 25 C.

Band4 S21, Log Scale

0

-10

-10

-20

-30

-50

-60

0.1

Frequency (GHz)

0 -10 -10 -20 -30 -50 -60 0.1 1 10 Frequency (GHz)

Band7 S21, Log Scale

Test conditions unless otherwise specified:  $V_{dd} = +5 V$ , T = 25 C.

Input IP3 Thru Path, Log Scale

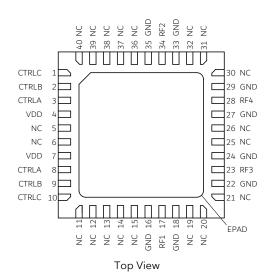

# **Pin Description**

| Pin Number                                      | Pin Name | Description                                                                                                                              |  |

|-------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17                                              | RF1      | RF pin. Can be used as input or output. DC coupled; external DC bloc capacitors are required.                                            |  |

| 34                                              | RF2      | RF pin. Can be used as input or output. DC coupled; external DC block capacitors are required.                                           |  |

| 23                                              | RF3      | RF pin. Can be used as input or output. DC coupled; external DC bloc capacitors are required. If unused should be left open              |  |

| 28                                              | RF4      | RF pin. Can be used as input or output. DC coupled; external DC block capacitors are required.                                           |  |

| 1, 10                                           | CTRLC    | Control C input. Two CTRLC pins are shorted internally. Using one of them is sufficient for controlling filter state.                    |  |

| 2, 9                                            | CTRLB    | Control B input. Two CTRLB pins are shorted internally. Using one of them is sufficient for controlling filter state.                    |  |

| 3, 8                                            | CTRLA    | Control A input. Two CTRLA pins are shorted internally. Using one of them is sufficient for controlling filter state.                    |  |

| 4, 7                                            | VDD      | Supply input.                                                                                                                            |  |

| 5, 6, 11-15, 19-21,<br>25, 26, 30-32, 36-<br>40 |          | These pins are not internally connected. Can be grounded on the PCB.                                                                     |  |

| 16, 18, 22, 24, 27,<br>29, 33, 35               | GND      | Ground.                                                                                                                                  |  |

| 41                                              | EPAD     | Exposed Pad on the bottom of the package should be connected to ground with multiple number of vias to reduce the inductance to the GND. |  |

9 of 12

#### **Control Interface**

| CTRLA | CTRLB | CTRLC | Filter Bank State     |

|-------|-------|-------|-----------------------|

| LOW   | LOW   | LOW   | Band1                 |

| LOW   | HIGH  | HIGH  | Band2                 |

| LOW   | LOW   | HIGH  | Band3                 |

| HIGH  | LOW   | HIGH  | Band4                 |

| LOW   | HIGH  | LOW   | Band5                 |

| HIGH  | LOW   | LOW   | Band6                 |

| HIGH  | HIGH  | LOW   | Band7                 |

| HIGH  | HIGH  | HIGH  | External Bypass State |

### **Applications Information**

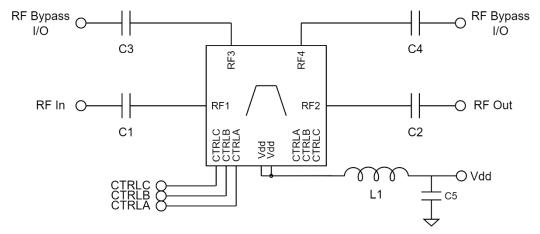

Signal entering from RF1 pins goes into 8 selectable paths. 7 of these paths are fixed frequency band pass filters and the 8<sup>th</sup> path is routed to RF3 pin. Symmetrical architecture lies in between RF2 and RF4 pins. Thus, RF3 and RF4 pins can be used to add an off chip thru path on the PCB. This will allow user to add bypass feature to the filterbank. Alternatively, an 8<sup>th</sup> filter can be connected in between RF3 and RF4 pins. Similarly, RF3 and RF4 pins can be used to connect an alternative filterbank. This allows user to create filterbank configurations with higher filter count in a modular architecture.

Typical application schematic to operate the filterbank is given below.

C1, C2, C3 and C4 are DC block capacitors. It is recommended to use wideband low loss DC block capacitors to achieve the best performance. Using low profile capacitors is also possible, which will result in additional loss. If RF3 and RF4 pins are not used, then using C3 and C4 is not required.

L1 and C5 are used to filter out the ripples and unwanted signal coming from the Vdd supply and providing an RF isolation between filterbank and Vdd supply to avoid RF signals leaking into Vdd. Using capacitors in parallel to C5 and choosing a wideband RF choke for L1 will improve better isolation performance. Similarly, using RC filtering on CTRL lines can improve performance. If these topics are of no concern, then filterbank can be operated without L1 and C5. Filterbank can be supplied in alternative packages and custom housings.

All measurement results presented on this document are gathered with connectorized EVB, where RF1 is input and RF2 is the output.

10 of 12

S21 data is de-embedded to eliminate the PCB trace loss and coaxial connector transition effects.

## **Absolute Maximum Ratings**

| Parameter                            | Value/Range   |

|--------------------------------------|---------------|

| Supply Voltage (Vdd)                 | TBD           |

| VCTRL (CTRLA, CTRLB, CTRLC)          | TBD           |

| Supply Current Idd                   | TBD           |

| Control Current (CTRLA, CTRLB, CTRLC | TBD           |

| Storage Temperature                  | −55 to +125°C |

Operation of this device outside the parameter ranges given above may cause damage. These parameters should not be applied simultaneously.

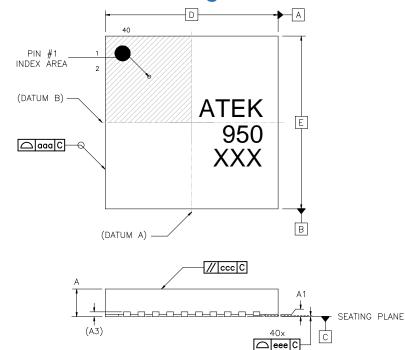

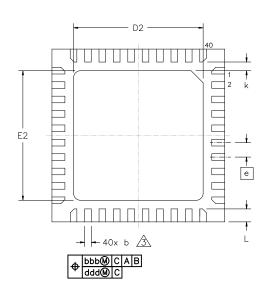

# **Mechanical and Marking Information**

NOTES:

1) ALL DIMENSIONS IN MM

2) DIMENSIONING AND TOLERANCING PER ASME Y14.5—2009

2) DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS

MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL

TO

| SYMBOL | MIN      | MAX  | SYMBOL | MIN  | MAX  |

|--------|----------|------|--------|------|------|

| A, V   | 0.80     | 1.00 | E2     | 4.40 | 4.60 |

| A, W   | 0.70     | 0.80 | е      | 0.50 | BSC  |

| A, L   | 1.40     | 1.70 | k      | 0.20 | -    |

| A1     | 0.00     | 0.05 | L      | 0.40 | 0.50 |

| A3     | 0.20 REF |      | ۵۵۵    | 0.10 |      |

| b      | 0.18     | 0.30 | bbb    | 0.:  | 10   |

| D      | 6.00 BSC |      | CCC    | 0.10 |      |

| D2     | 4.40     | 4.60 | ddd    | 0.0  | 05   |

| E      | 6.00     | BSC  | eee    | 0.0  | 98   |

### **Handling Precautions**

#### **Contact Information**

For the latest specifications, additional product information, support, and sales.

Web: <u>www.atekmidas.com</u> Tel: +90-212-483-71-67

Email: <a href="mailto:support@atekmidas.com">support@atekmidas.com</a>

#### **Notice**

This document and its contents are property of ATEK MIDAS. ATEK MIDAS has the right to change the document at any time without notice. ATEK MIDAS distributes this document as a service to its customers. ATEK MIDAS supports its customers to help them create market leader products. Customer is responsible from choosing the product and the configuration the product. This document is provided `as is` and does not provide any warranty.

Customer is responsible for the usage of this document, the information provided in the document and the usage of products. ATEK MIDAS shall have no responsibility from the customer products, customer applications and doings of customers.

#### **Revisions**

| Revision No | Revision Date | Revision Reason           | Section / Page No  |

|-------------|---------------|---------------------------|--------------------|

| 1.0         | 07.12.2021    | Initial Release           |                    |

| 1.1         | 25.01.2022    | Drawing and Plots Revised | 3/7, 4/7, 5/7, 6/7 |

| 1.2         | 01.11.2023    | Format and Content Fixed  |                    |

| 1.3         | 10.11.2023    | Format and Content Fixed  |                    |